LLNL researchers have developed a fabrication process for creating 3D random interdigitated architectures of anodes and cathodes, eliminating the need for a membrane to separate them. This approach is similar to the repeating interdigitated multi-electrode architectures that also were developed at LLNL.

Keywords

- Show all (74)

- Photoconductive Semiconductor Switches (PCSS) (9)

- Electric Grid (8)

- Imaging Systems (8)

- Carbon Utilization (6)

- Semiconductors (6)

- Materials for Energy Products (4)

- Optical Switches (4)

- Additive Manufacturing (3)

- Power Electronics (3)

- Sensors (3)

- Spectrometers (3)

- Computing (2)

- Direct Air Capture (2)

- Optical Sensors (2)

- Particle Accelerators (2)

- Simulation (2)

- Precision Engineering (1)

- (-) 3D Printing (2)

- (-) MEMS Sensors (2)

- (-) Synthesis and Processing (2)

LLNL researchers have developed a Li-Sn-Zn ternary alloy and its method of production. Instead of traditional alloying techniques, the alloy was synthesized using mechanical alloying (high energy ball milling). With high purity elemental powders of lithium, tin and zinc, LLNL researchers were able to prepare Li60Sn20Zn20 as well as Li70Sn20Zn10 nanopowders.

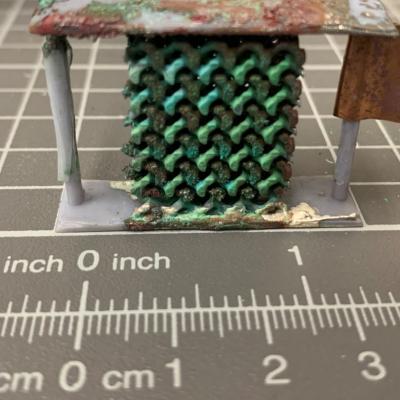

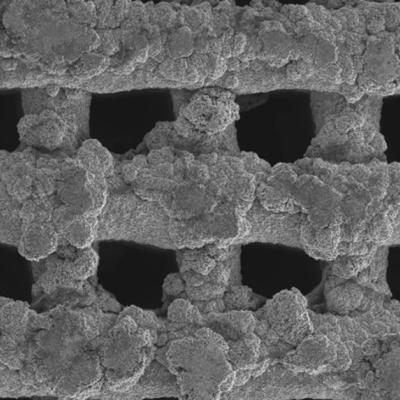

Improving the active material of the Zn anode is critical to improving the practicality of Zn-MnO2 battery technology. LLNL researchers have developed a new category of 3D structured Zn anode using a direct-ink writing (DIW) printing process to create innovative hierarchical architectures. The DIW ink, which is a gel-based mixture composed of zinc metal powder and organic binders, is extruded…

CMI—a DOE Energy Innovation Hub—is a public/private partnership led by the Ames Laboratory that brings together the best and brightest research minds from universities, national laboratories (including LLNL), and the private sector to find innovative technology solutions to make better use of materials critical to the success of clean energy technologies as well as develop resilient and secure…

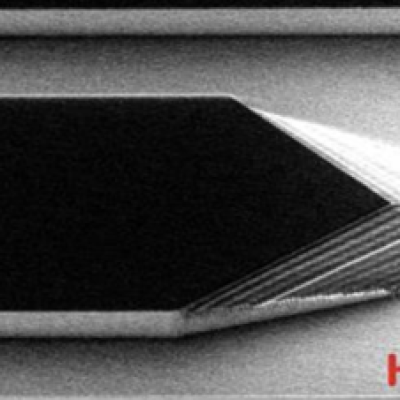

For this method, a Silicon on Insulator (SOI) wafer is used to tailor etch rates and thickness in initial steps of the process. The simple three step process approach is comprised of grayscale lithography, deep reactive-ion etch (DRIE) and liftoff of the SOI wafer. The liftoff process is used to dissolve the insulating layer, thus separating sections of the wafer as individual silicon…

LLNL has developed a compact and low-power cantilever-based sensor array, which has been used to detect various vapor-phase analytes. For further information on the latest developments, see the article "Sniffing the Air with an Electronic Nose."