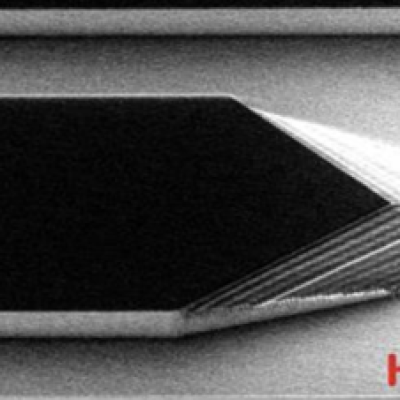

For this method, a Silicon on Insulator (SOI) wafer is used to tailor etch rates and thickness in initial steps of the process. The simple three step process approach is comprised of grayscale lithography, deep reactive-ion etch (DRIE) and liftoff of the SOI wafer. The liftoff process is used to dissolve the insulating layer, thus separating sections of the wafer as individual…

Keywords

- (-) Show all (240)

- Additive Manufacturing (55)

- Instrumentation (41)

- Synthesis and Processing (21)

- Sensors (14)

- Diagnostics (11)

- Imaging Systems (9)

- Photoconductive Semiconductor Switches (PCSS) (9)

- 3D Printing (8)

- Carbon Utilization (7)

- Electric Grid (7)

- Materials for Energy Products (7)

- Semiconductors (7)

- Substrate Engraved Meta-Surface (SEMS) (7)

- Therapeutics (7)

- Compact Space Telescopes (6)

- Brain Computer Interface (BCI) (5)

- Data Science (5)

- Diode Lasers (5)

- Optical Switches (5)

- Laser Materials Processing (4)