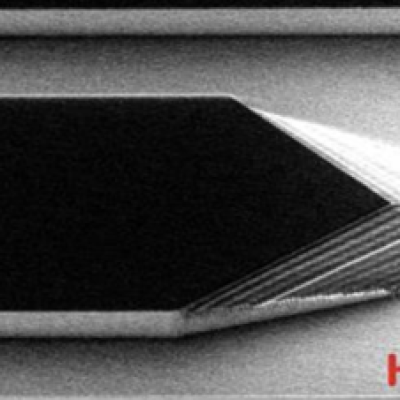

For this method, a Silicon on Insulator (SOI) wafer is used to tailor etch rates and thickness in initial steps of the process. The simple three step process approach is comprised of grayscale lithography, deep reactive-ion etch (DRIE) and liftoff of the SOI wafer. The liftoff process is used to dissolve the insulating layer, thus separating sections of the wafer as individual…

Keywords

- Show all (53)

- Imaging Systems (9)

- Photoconductive Semiconductor Switches (PCSS) (9)

- Semiconductors (7)

- Optical Switches (5)

- Power Electronics (4)

- Additive Manufacturing (2)

- Computing (2)

- Electric Grid (2)

- Sensors (2)

- Spectrometers (2)

- Analysis (1)

- Brain Computer Interface (BCI) (1)

- Compact Space Telescopes (1)

- Instrumentation (1)

- MEMS Sensors (1)

- Optical Sensors (1)

- Particle Accelerators (1)

- (-) 3D Electronics (1)

- (-) Quantum Science (1)

Technology Portfolios

Image

LLNL has developed a method of extending device lifetimes by imprinting into the device a shape that excludes specific vibrational modes, otherwise known as a phononic bandgap. Eliminating these modes prevents one of the primary energy loss pathways in these devices. LLNL’s new method enhances the coherence of superconducting circuits by introducing a phononic bandgap around the system’s…