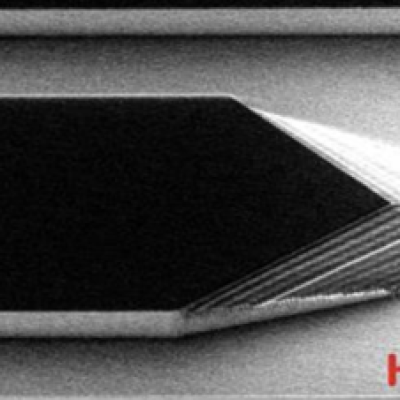

For this method, a Silicon on Insulator (SOI) wafer is used to tailor etch rates and thickness in initial steps of the process. The simple three step process approach is comprised of grayscale lithography, deep reactive-ion etch (DRIE) and liftoff of the SOI wafer. The liftoff process is used to dissolve the insulating layer, thus separating sections of the wafer as individual…

Keywords

- Show all (53)

- Imaging Systems (9)

- Photoconductive Semiconductor Switches (PCSS) (9)

- Semiconductors (7)

- Optical Switches (5)

- Power Electronics (4)

- Additive Manufacturing (2)

- Computing (2)

- Electric Grid (2)

- Sensors (2)

- Spectrometers (2)

- Analysis (1)

- Brain Computer Interface (BCI) (1)

- Compact Space Telescopes (1)

- Instrumentation (1)

- MEMS Sensors (1)

- Optical Sensors (1)

- Quantum Science (1)

- (-) 3D Electronics (1)

- (-) Particle Accelerators (1)

Technology Portfolios

Image

The approach is to build a high voltage insulator consisting of two materials: Poly-Ether-Ether-Ketone (“PEEK”) and Machinable Ceramic (“MACOR”). PEEK has a high stress tolerance but cannot withstand high temperatures, while MACOR has high heat tolerance but is difficult to machine and can be brittle. MACOR is used for the plasma-facing surface, while PEEK will handle the…