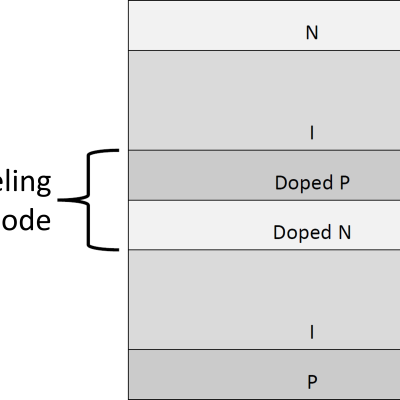

LLNL developed a novel SOS diode structure starting with a n-type silicon wafer. On the appropriate sides of the wafer, donor and acceptor dopants with specifically designed and optimized concentration profiles are diffused in the structure. Crucially, an extra n-region is introduced to the structure to address pre-pulses. The result is a SOS diode with an optimized p+/p/n-…

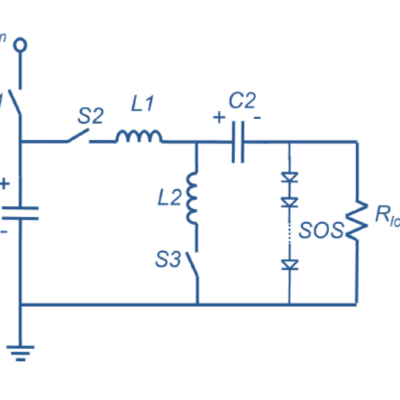

Instead of producing individual DSRDs and bonding them, Tunnel DSRD's entire stack structure is grown epitaxially on a n- or p-type silicon wafer, resulting in a novel, “monolithic” stacked DSRD. A tunnel diode is essentially a diode with very highly doped p and n regions such that the reverse breakdown voltage is 200 meV or lower.

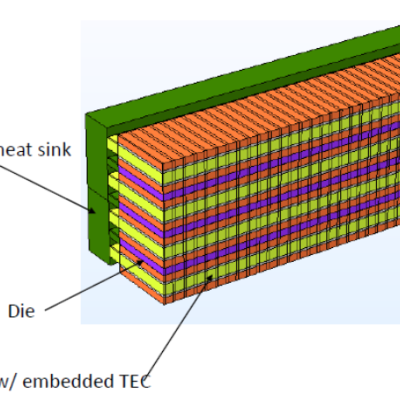

For cooling a high power device, the novel approach is to use a thermoelectric cooler (TEC)-based embedded substrate with proper selection of the TEC material as an active cooler. The packaging configuration of TEC allows cooling the entire die without the use of a fluid. The process is compatible with the thin film TEC material. Standard semiconductor processes can be used…

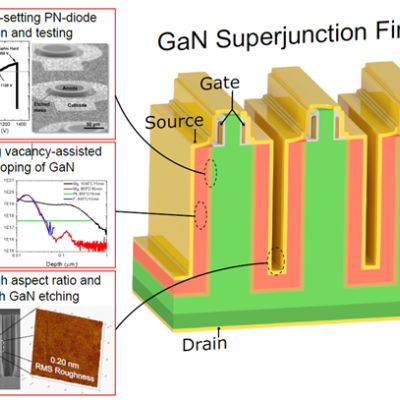

The approach is to use Charge Balance Layers (CBLs) to create a superjunction device in wide bandgap materials. These CBLs enable the device to effectively spread the electric field over 2- or 3-dimensions within a semiconductor voltage sustaining layer instead of 1-dimension, thereby increasing the maximum voltage a device is capable of withstanding. The challenge of using CBLs is…