LLNL developed a novel SOS diode structure starting with a n-type silicon wafer. On the appropriate sides of the wafer, donor and acceptor dopants with specifically designed and optimized concentration profiles are diffused in the structure. Crucially, an extra n-region is introduced to the structure to address pre-pulses. The result is a SOS diode with an optimized p+/p/n-…

Keywords

- Show all (239)

- Additive Manufacturing (54)

- Instrumentation (41)

- Synthesis and Processing (21)

- Sensors (14)

- Diagnostics (12)

- Imaging Systems (9)

- Photoconductive Semiconductor Switches (PCSS) (9)

- 3D Printing (8)

- Electric Grid (7)

- Materials for Energy Products (7)

- Substrate Engraved Meta-Surface (SEMS) (7)

- Therapeutics (7)

- Carbon Utilization (6)

- Compact Space Telescopes (6)

- Brain Computer Interface (BCI) (5)

- Data Science (5)

- Diode Lasers (5)

- Optical Switches (5)

- Laser Materials Processing (4)

- (-) Semiconductors (7)

The essence of this invention is a method that couples network architecture using neural implicit representations coupled with a novel parametric motion field to perform limited angle 4D-CT reconstruction of deforming scenes.

LLNL researchers have invented an ultrafast PCSS to drive a high-power laser diode with arbitrary pulse widths. These devices operate by supplying a high voltage (>10 kV) to one side of the switch. A short pulse of light illuminates the semiconductor, instantly turning it from highly resistive to highly conductive. Ultrawide bandgap (UWBG) semiconductors are used to achieve sub-…

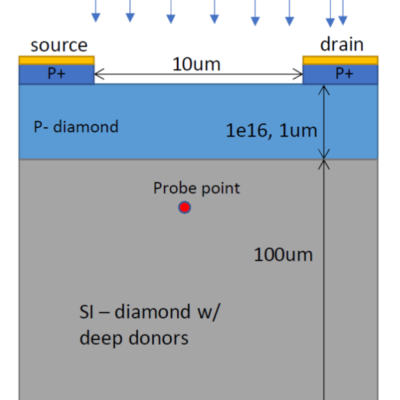

LLNL’s novel approach is to use diamond substrates with the desired donor (nitrogen) and acceptor (boron) impurities. In order to optically activate these deep impurities, the invention requires at least one externally or internally integrated light source. The initial exposure to light can set up the desired conduction current, after which the light source could be turned…

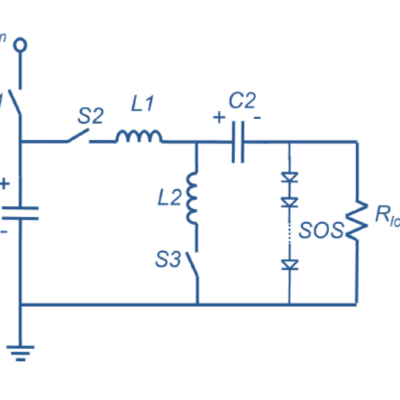

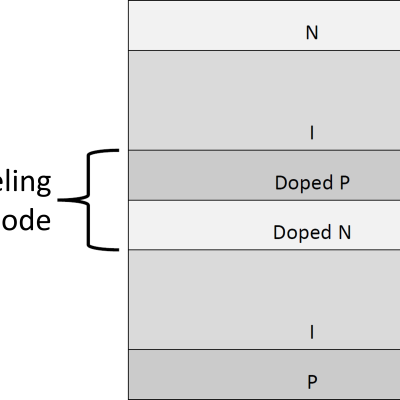

Instead of producing individual DSRDs and bonding them, Tunnel DSRD's entire stack structure is grown epitaxially on a n- or p-type silicon wafer, resulting in a novel, “monolithic” stacked DSRD. A tunnel diode is essentially a diode with very highly doped p and n regions such that the reverse breakdown voltage is 200 meV or lower.

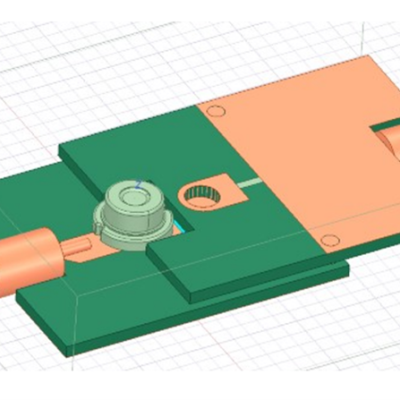

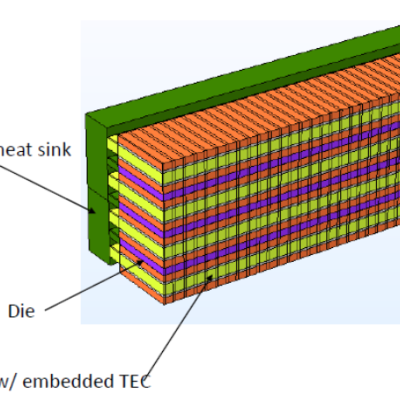

For cooling a high power device, the novel approach is to use a thermoelectric cooler (TEC)-based embedded substrate with proper selection of the TEC material as an active cooler. The packaging configuration of TEC allows cooling the entire die without the use of a fluid. The process is compatible with the thin film TEC material. Standard semiconductor processes can be used…

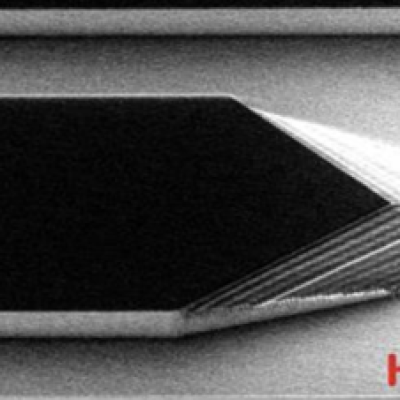

For this method, a Silicon on Insulator (SOI) wafer is used to tailor etch rates and thickness in initial steps of the process. The simple three step process approach is comprised of grayscale lithography, deep reactive-ion etch (DRIE) and liftoff of the SOI wafer. The liftoff process is used to dissolve the insulating layer, thus separating sections of the wafer as individual…

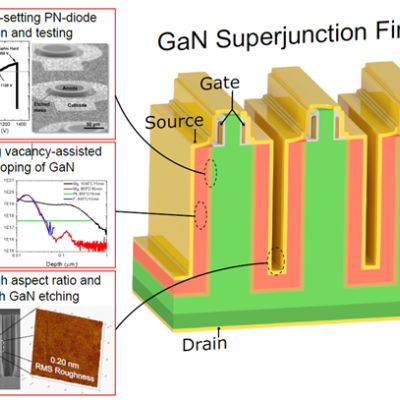

The approach is to use Charge Balance Layers (CBLs) to create a superjunction device in wide bandgap materials. These CBLs enable the device to effectively spread the electric field over 2- or 3-dimensions within a semiconductor voltage sustaining layer instead of 1-dimension, thereby increasing the maximum voltage a device is capable of withstanding. The challenge of using CBLs is…

To solve these challenges using new and existing CT system designs, LLNL has developed an innovative software package for CT data processing and reconstruction. Livermore Tomography Tools (LTT) is a modern integrated software package that includes all aspects of CT modeling, simulation, reconstruction, and analysis algorithms based on the latest research in the field. LTT contains the most…

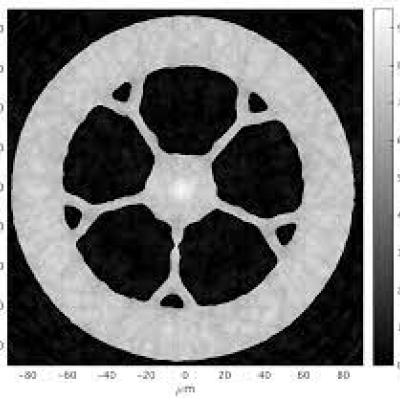

The LLNL method for optimizing as built optical designs uses insights from perturbed optical system theory and reformulates perturbation of optical performance in terms of double Zernikes, which can be calculated analytically rather than by tracing thousands of rays. A new theory of compensation is enabled by the use of double Zernikes which allows the performance degradation of a perturbed…